Los AMD basados en Zen 3 tendrán caché L3 compartida y se rumorean incrementos del 10% en IPC

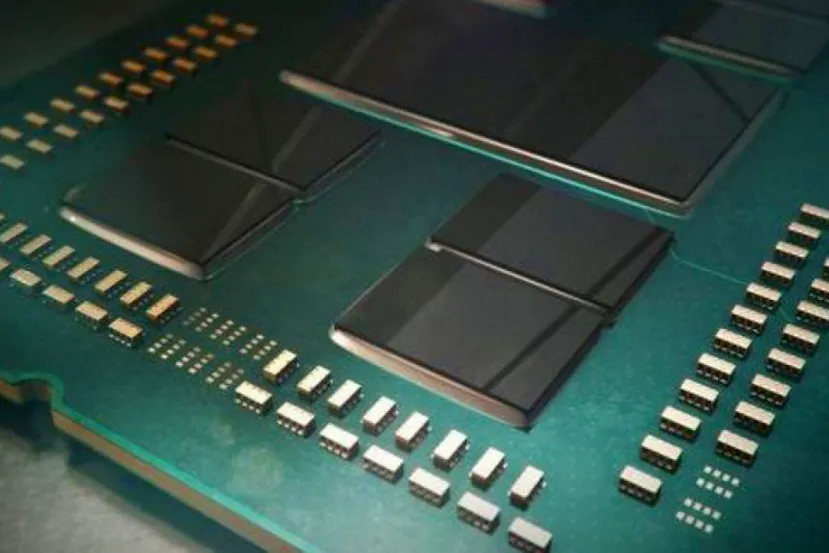

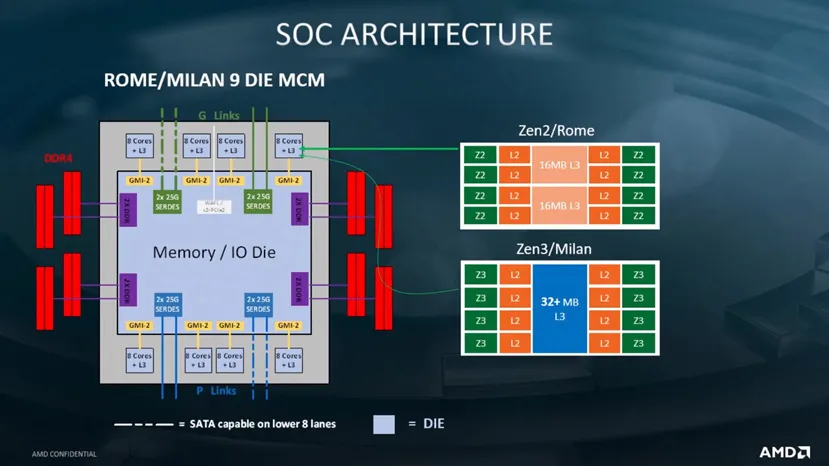

por Sergio San Joaquín 2AMD ha dejado ver algunos detalles de su nueva arquitectura Zen 3 en la “Innovators Highlights Epyc conference”, una diapositiva ha mostrado diversos cambios en la arquitectura que buscan principalmente reducir la latencia utilizando una caché compartida dentro de sus chiplets.

En Zen 2, AMD utilizó los conocidos como CCX, grupos de 4 cores que unidos a otro CCX formaban un CCD de 8 núcleos, cada grupo de 4 cores (CCX) tenía su propia caché L3 de 16 MB (4MB por cada núcleo), pero, la caché L3 no era compartida entre todos los núcleos del procesador.

Dependiendo del número de núcleos de cada procesador en concreto, se podían utilizar un CCD (hasta 8 núcleos) o añadir más para aquellos procesadores como el Ryzen 9 3900X (12 núcleos) o el inminente AMD Ryzen 9 3950X de 16 núcleos. Cada CCD se comunica con el I/O DIE para completar el famoso sistema de chiplets de AMD.

La diapositiva en cuestión nos deja claro el primer cambio bien visible, y es la unificación de la caché L3 que será compartida por todos los CCD, el objetivo es simple, reducir la latencia al tener menor tiempo de acceso a la memoria caché L3.

Por otro lado, fuentes cercanas al medio de comunicación redgamingtech aseguran un incremento de aproximadamente un 10% de IPC (instrucciones por ciclo de reloj) respecto a Zen 2, e incluso se rumorea que ya hay algún Engineering Sample con incrementos de 200 Mhz por cada núcleo.

Sin embargo, la diapositiva elimina en cierto modo el rumor que sostenía que AMD estaba trabajando en SMT-4, procesadores con 4 hilos de ejecución por cada núcleo.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!