ARM Cortex-X4: ¿Cómo Consigue Aumentar el Rendimiento en un 24%?

por Antonio Delgado Actualizado: 29/05/2023 2Nuevas CPU Armv9.2

Hemos asistido presencialmente a los ARM Client Tech Days, un evento de ARM donde la compañía ha dado a conocer todas las novedades a nivel técnico de sus nuevas arquitecturas de núcleos de CPU y GPU que darán vida a las próximas generaciones de SoCs basados en ARM. En este artículo repasaremos todas las novedades en detalle de la parte de arquitectura de CPU.

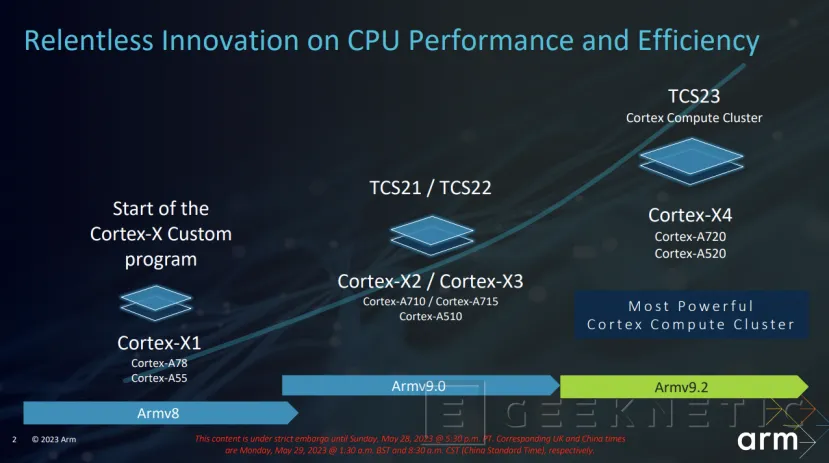

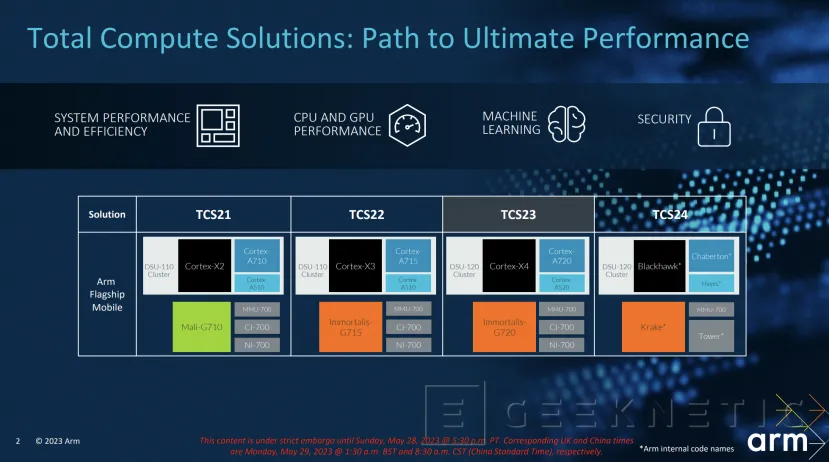

Tras el lanzamiento de los núcleos Cortex-X1 junto a los Cortex-A78 y Cortex-A55 que llegaron con la arquitectura Armv8, y su sucesora, las plataformas TCS21 y TCS22 con núcleos Cortex-X2 y Cortex-X3 de alto rendimiento acompañadas de los Cortex-A710/715 y Cortex-A510, ahora llega la plataforma TCS23 (Total Compute Solution) con nuevos núcleos de altas prestaciones, de rendimiento y de bajo consumo.

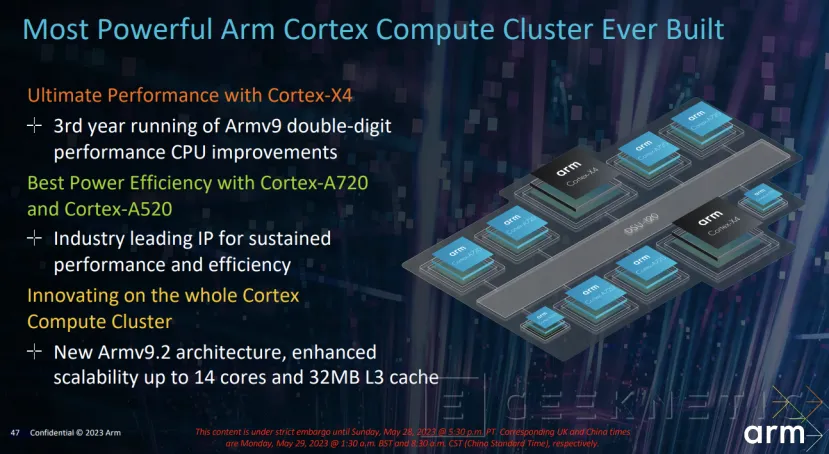

En concreto, la plataforma más potente de ARM hasta la fecha introduce los nuevos núcleos Cortex-X4 de máximo rendimiento, los Cortex-A720 de altas prestaciones y los Cortex-A520 de alta eficiencia, todos ellos basados en las instrucciones ARMv9.2.

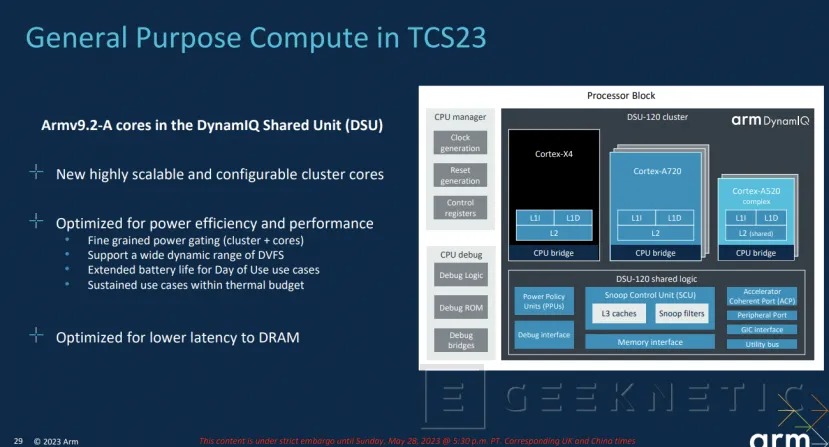

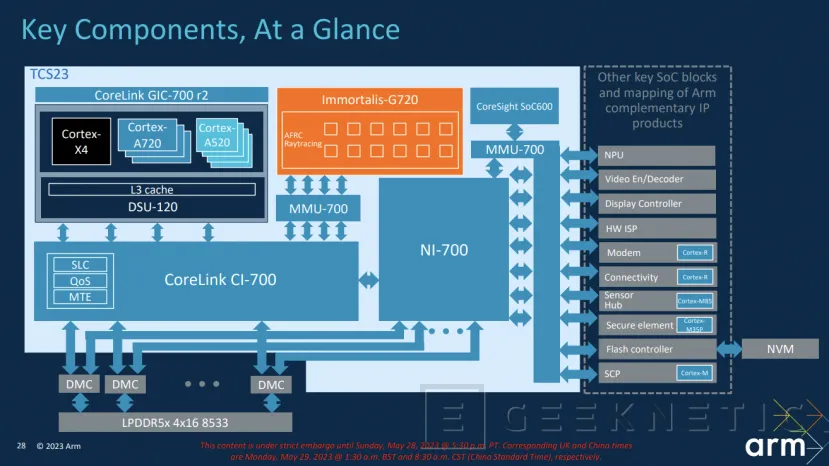

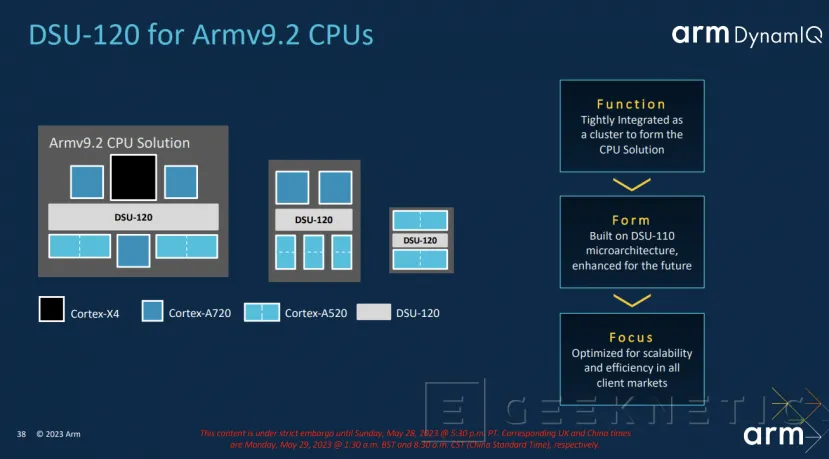

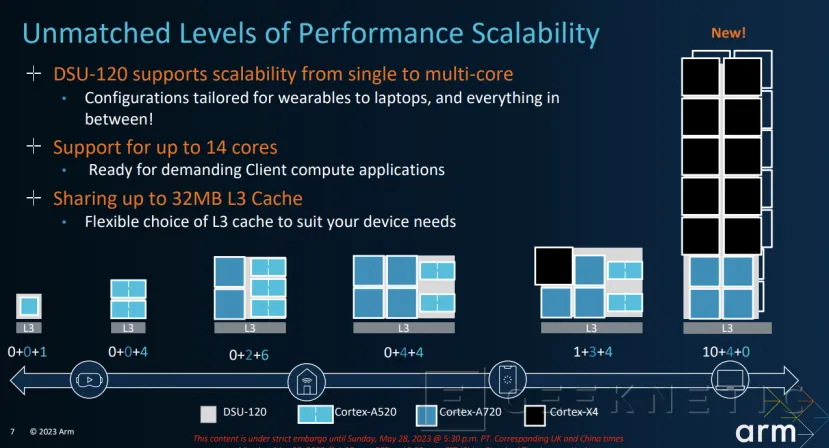

La TCS23 es un conjunto de todos los componentes que forman un SOC basado en estas arquitecturas, incluyendo los distintos núcleos, caché o GPU entre muchos otros. La distribución de núcleos es configurable por las compañía que diseñen sus procesadores con los nuevos núcleos de ARM, por ejemplo, una formada por un núcleo Cortex-X4, tres núcleos Cortex-A720 y cuatro Cortex-A520, aunque como veremos más adelante, las combinaciones son múltiples.

El nuevo diseño de núcleos Armv9.2 es altamente escalable y se pueden configurar con combinaciones de todo tipo, incluso soluciones formadas por múltiples núcleos de alto rendimiento Cortex-X4, o incluir más o menos núcleos de alta eficiencia, todo ello acompañado de nuevos diseños y tecnologías que consiguen una mayor eficiencia energética y más rendimiento como veremos a lo largo del artículo.

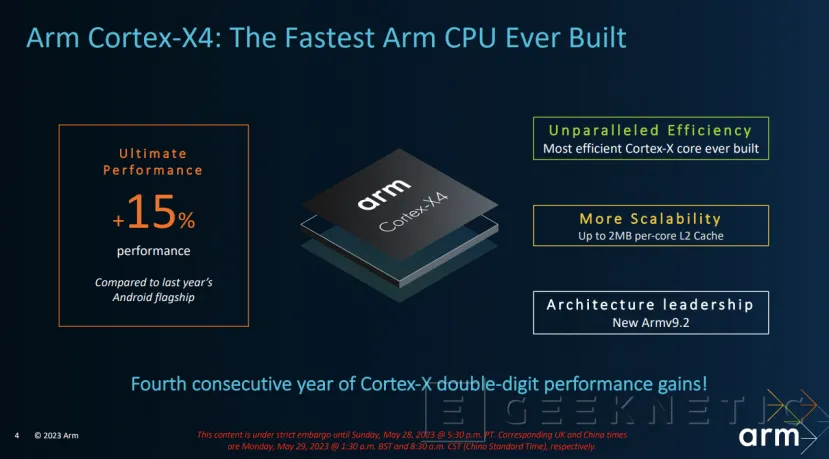

ARM Cortex-X4: El núcleo ARM más potente jamás creado

Empezamos viendo en detalle los núcleos más potentes de esta nueva generación, y de la propia historia de ARM: los ARM Cortex-X4.

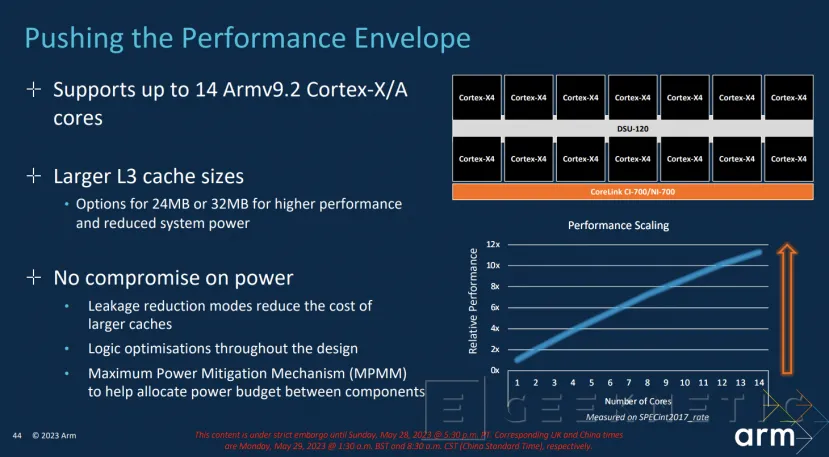

Estos núcleos están pensados para las tareas más pesadas y que requieren de un mayor rendimiento en un solo hilo, sin embargo, con esta nueva arquitectura se ha creado un diseño mucho más escalable con el que podremos tener procesadores de hasta 14 núcleos Cortex-X4, cada uno con hasta 2 MB de caché L2, tal y como veremos más adelante cuando entremos en detalle en los clústeres.

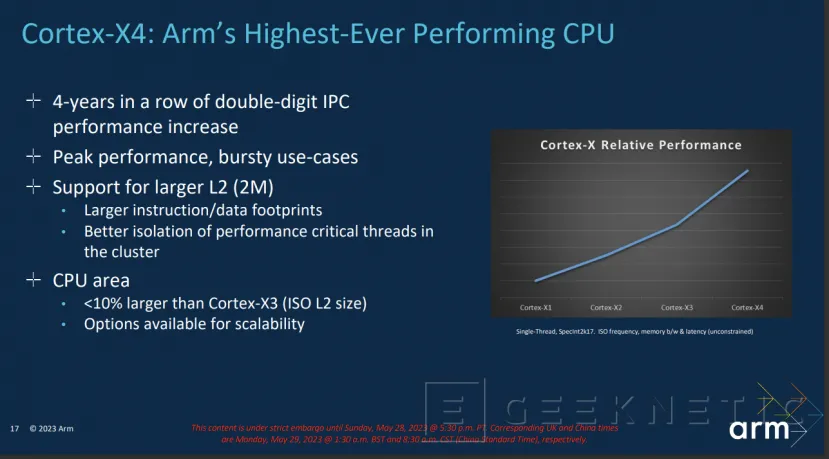

Los Cortex-X4 prometen un rendimiento un 15% superior al de la pasada generación de núcleos ARM y un 40% menos consumo, se trata del cuarto año consecutivo en el que ARM consigue cifras de dos dígitos de aumento de rendimiento respecto de las generaciones anteriores.

Soporta cachés L2 mayores de hasta 2 MB para permitir el procesamiento de instrucciones más grandes y ofrecer más rendimiento de manera independiente dentro del clúster de varios núcleos, todo ello con un tamaño de algo menos del 10% por encima del Cortex-X3 del pasado año.

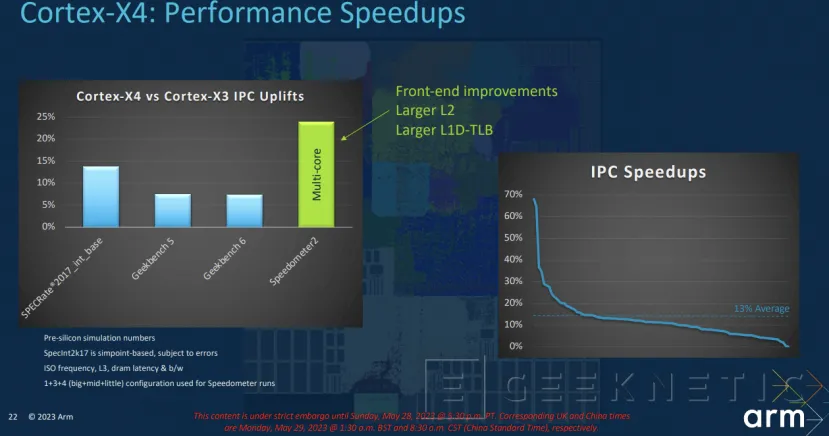

Según los datos de Speedometer2, hay un aumento del IPC (instrucciones por ciclo de reloj) del 24% respecto de la pasada generación, utilizando un único núcleo X4 en un clúster de 8 núcleos.

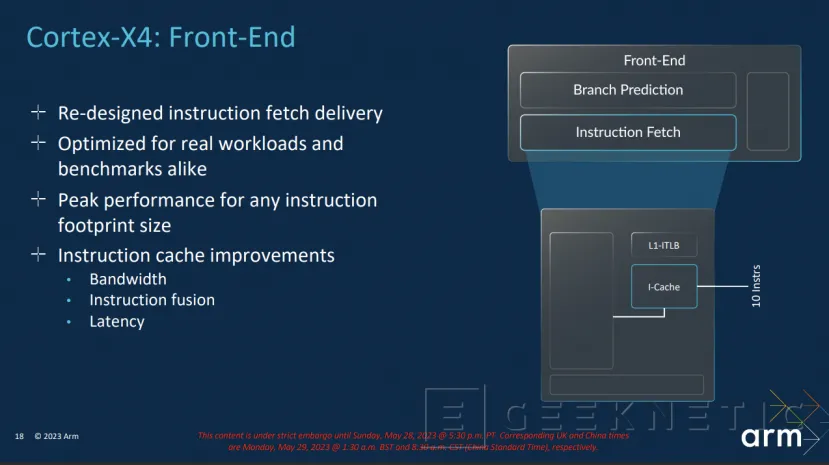

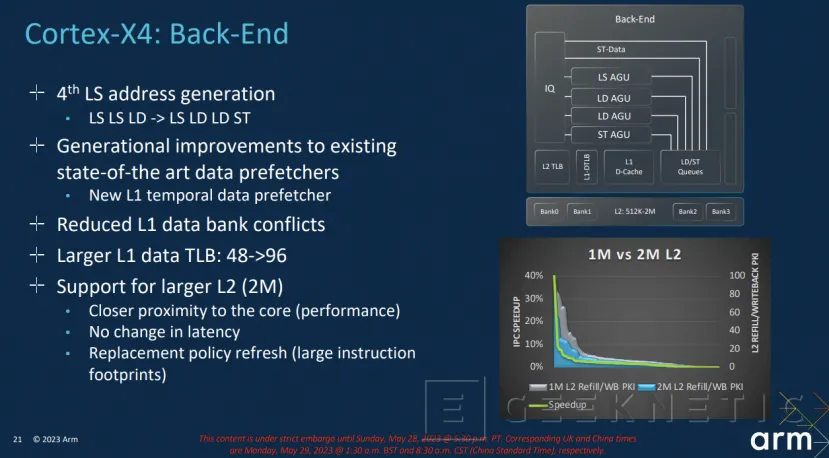

Si el pasado año, el lanzamiento de los Cortex X3 supuso mejorar la predicción de instrucciones en el Front-End, en esta ocasión el Cortex-X4 ha mejorado el ámbito de la búsqueda de instrucciones a ejecutar en casos de uso reales. También se ha mejorado la caché de instrucciones, con un aumento del ancho de banda, la fusión de instrucciones y reducción de la latencia.

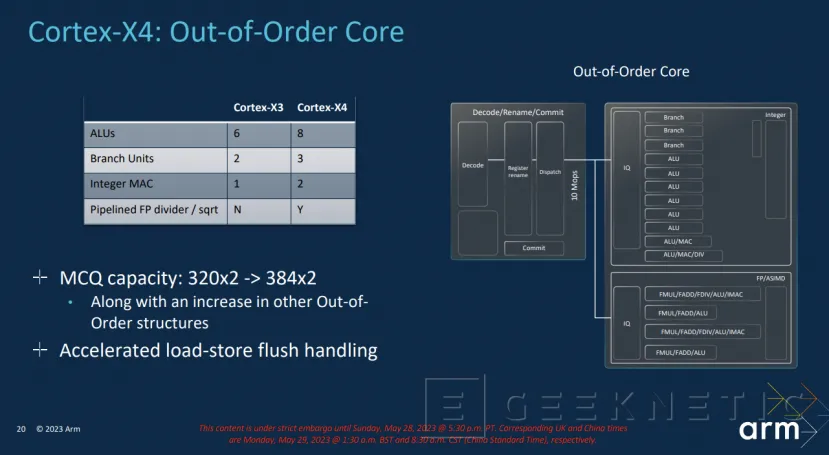

El Cortex-X4 aumenta el número de ALUS y de unidades de predicción. La tecnología "out-of-order Core" o ejecución dinámica, permite que las instrucciones no se procesen por su orden inicial, sino que se ejecutan dependiendo de la disponibilidad de los recursos del procesador y de los datos a los que tiene acceso. De esta manera, se aprovechan mejor los ciclos de reloj y el procesador no se queda en idle esperando a que se termine la instrucción previa tanto tiempo. En el Cortex-X4 se han aumentado las distintas estructuras enfocadas a optimizar este paradigma de ejecución.

Además de pasar de 1 MB a 2 MB de caché L2, la disposición de esta caché está ahora físicamente más cerca del núcleo, por lo que se consigue un mayor rendimiento sin que se aumente la latencia.

Ahora daremos un repaso a los núcleos para tareas multinúcleo de alto rendimiento que acompañarán a los Cortex-X4 en la mayoría de SoCs, los Cortex-A720.

ARM Cortex-A720: Se duplica la eficiencia y el rendimiento sostenido

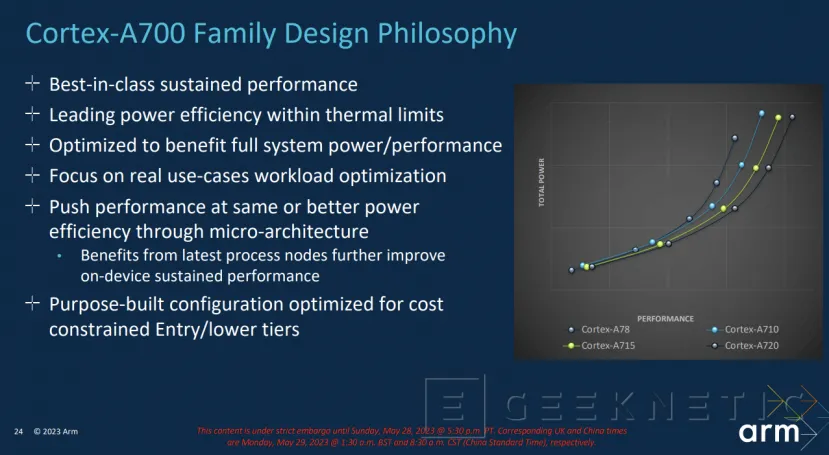

ARM se ha centrado en mejorar la eficiencia energética de sus núcleos Cortex-A720, orientados para tareas que requieren rendimiento en multinúcleo. En concreto, la compañía promete duplicar la eficiencia siguiendo con la estrategia que llevan siguiendo desde el lanzamiento de los Cortex-A78.

Si con los Cortex-X4 se busca el máximo rendimiento en tareas concretas, los Cortex-A720, y en general toda la familia A700, basa su existencia en mantener rendimiento multinúcleo en todo tipo de tareas de largo recorrido, es decir, que son capaces de mantener su rendimiento a lo largo del tiempo con temperaturas por debajo de los límites térmicos de los SoC.

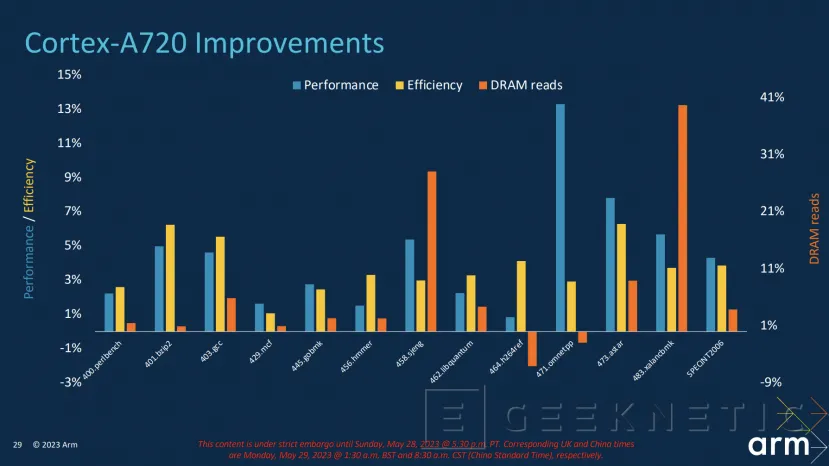

Cada nueva generación consigue más rendimiento y eficiencia, de hecho, estos Cortex-A720 consiguen más rendimiento que los Cortex-A710 consumiendo menos, y superan a los Cortex-A715 con el mismo nivel de consumo.

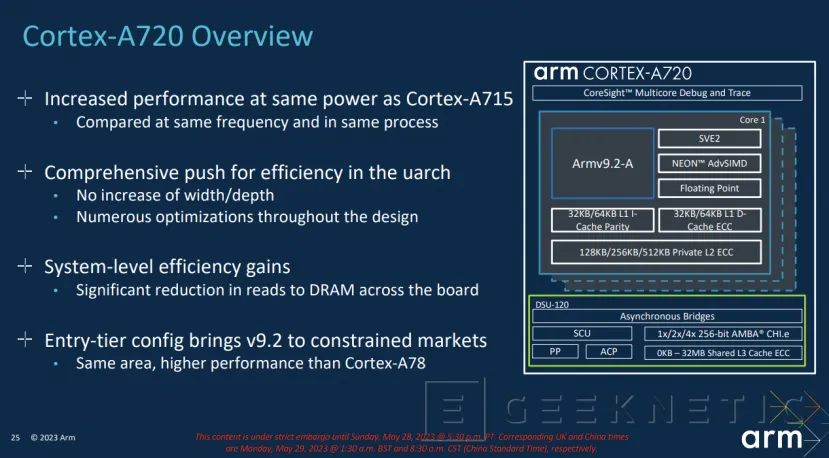

A misma frecuencia y usando el mismo nodo de fabricación, ARM promete más rendimiento con el mismo consumo que el Cortex-A715.

Se ha mejorado el diseño para conseguir distintas optimizaciones de energía y prestaciones sin aumentar el tamaño de los núcleos, mejorando también la latencia y reduciendo las lecturas a memoria.

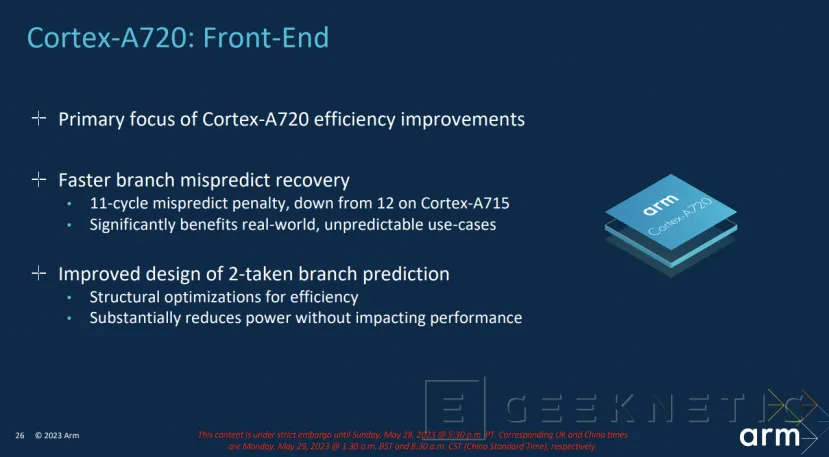

Las mejoras en el diseño interno permiten un menor número de penalizaciones en el sistema de predicción de instrucciones respecto de la arquitecturas Cortex-A715. En concreto, la penalización ante una predicción errónea es de 11 ciclos de reloj en vez de los 12 de su predecesora, lo que mejora el rendimiento en aplicaciones convencionales donde no se pueda predecir qué instrucciones serán las siguientes. Solamente con este cambio se connsigue un 1% más de rendimiento.

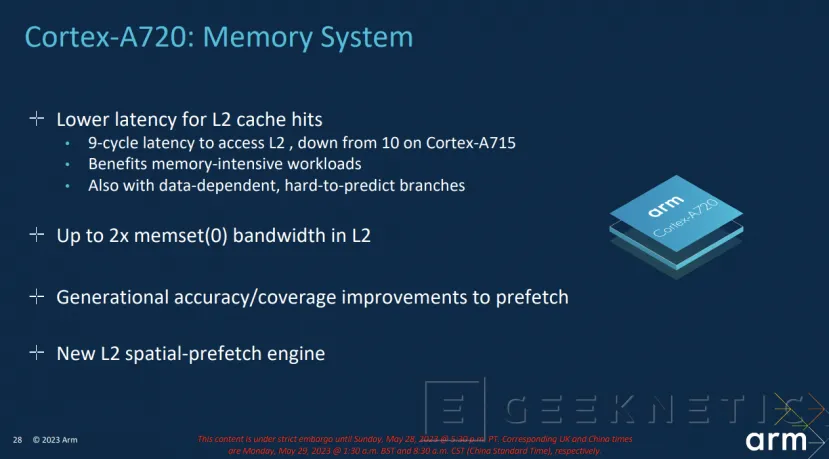

También se ha reducido de 10 a 9 los ciclos de latencia necesarios para acceder a la caclé L2. Esto mejora el rendimiento en aplicaciones muy dependientes de la memoria donde es difícil la predicción de las instrucciones y datos necesarios.

El sistema de prefetch de predicción de datos se ha mejorado, integrando un sistema similar al utilizado en los núcleos Cortex-X4 de mayor rendimiento.

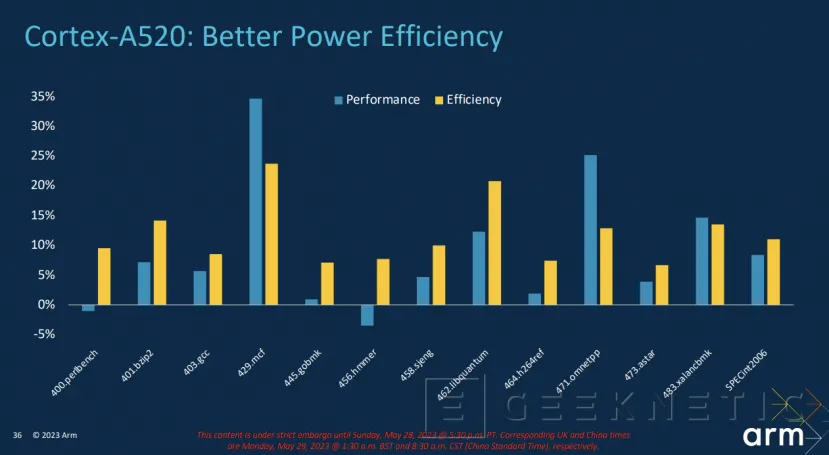

ARM Cortex-A520: Aún más eficiencia

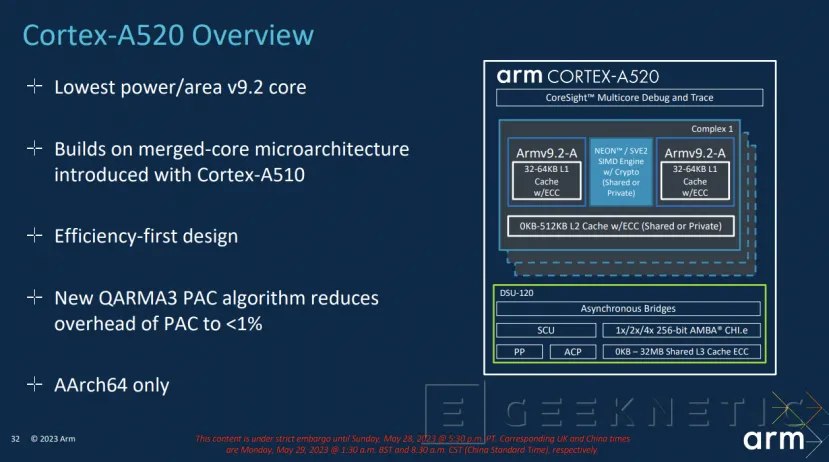

Los núcleos más modestos de la arquitectura big.LITTLE de esta nueva generación Armv9.2 también se actualizan con los nuevos ARM Cortex-A520.

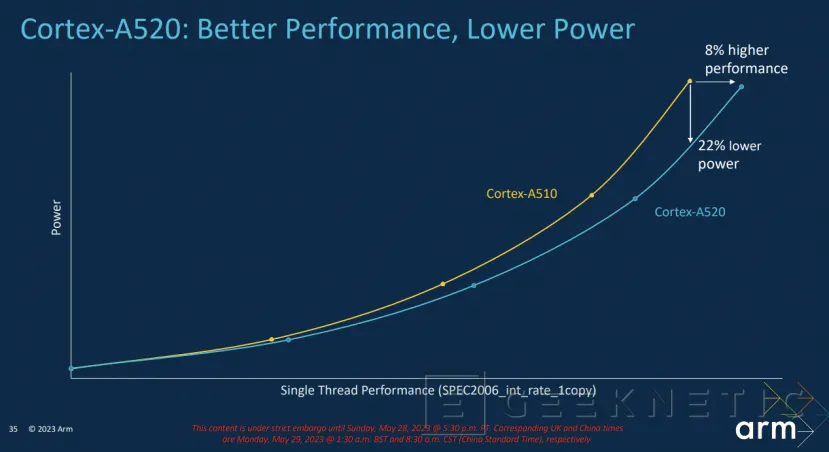

Estos núcleos de la línea A500 se orientan a tareas en segundo plano y otras con bajos requisitos de potencia, consiguiendo unos consumos muy inferiores y mayores eficiencias energéticas. En este caso concreto, los Cortex-A520 prometen una eficiencia energética un 22% superior a la de los Cortex-A510.

Se trata, por tanto, de los núcleos más eficientes Armv9.2, manteniendo el diseño de núcleos compartidos que ya se utilizó en la arquitectura Cortex-A510, eso supone que cada par de núcleos comparten ciertos elementos como la Caché L2 (hasta 512 KB con ECC), mientras que cada uno de ellos tiene su propio sistema de hasta 64KB de caché L1 con corrección de errores.

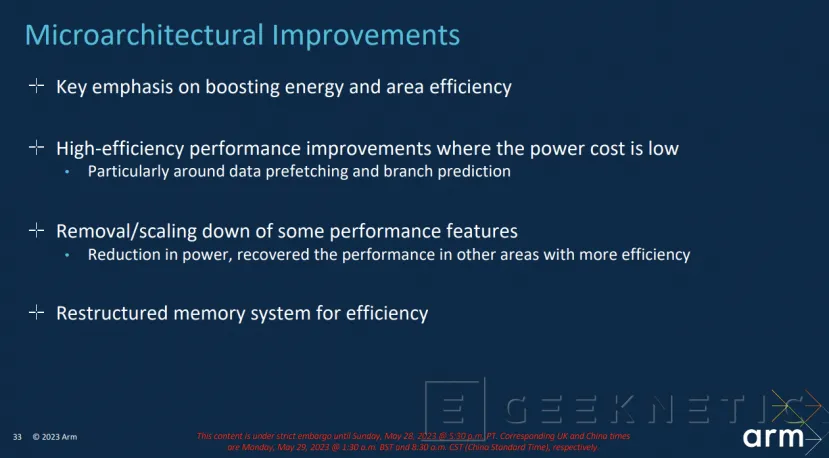

A nivel de mejoras de rendimiento y eficiencia, se han mejorado el sistema de predicción, uno de los aspectos donde es posible mejorar prestaciones sin aumentar consumo. También se ha reestructurado el sistema de memoria para mejorar la eficiencia y se han reducido ciertas prestaciones para centrarse en un menor consumo.

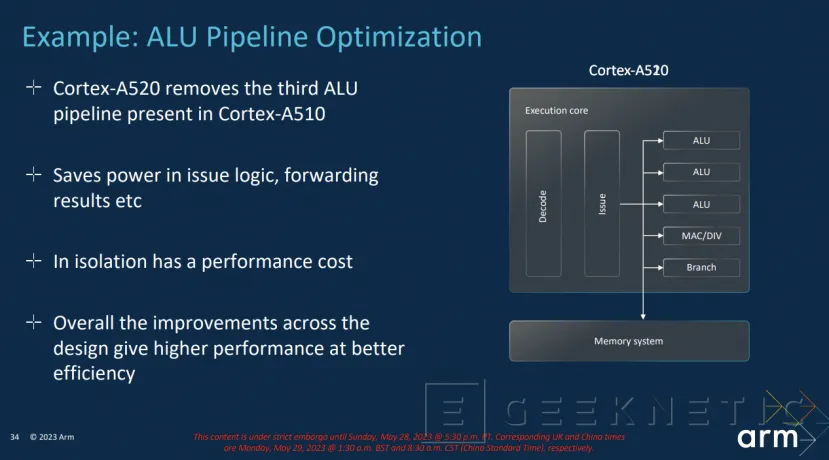

En concreto, perdemos una ALU de las tres que tenían los Cortex-A510 pasando a únicamente 2. La razón no es otra que priorizar la eficiencia reduciendo el consumo, pero también permite aprovechar el espacio que queda libre para mejorar el rendimiento. Por tanto, aunque se pierda algo de prestaciones en esa zona, en global, el núcleo Cortex-A520 ofrece mayor rendimiento con mejor eficiencia.

ARM nos habla de unas cifras de un 8% más de rendimiento al mismo nivel de energía, pero un 22% menos de energía necesaria para mantener el mismo nivel de rendimiento que el Cortex-A510.

De hecho, en la mayoría de casos podemos ver mejoras de rendimiento y de eficiencia en los distintos test de rendimiento que han ejecutado.

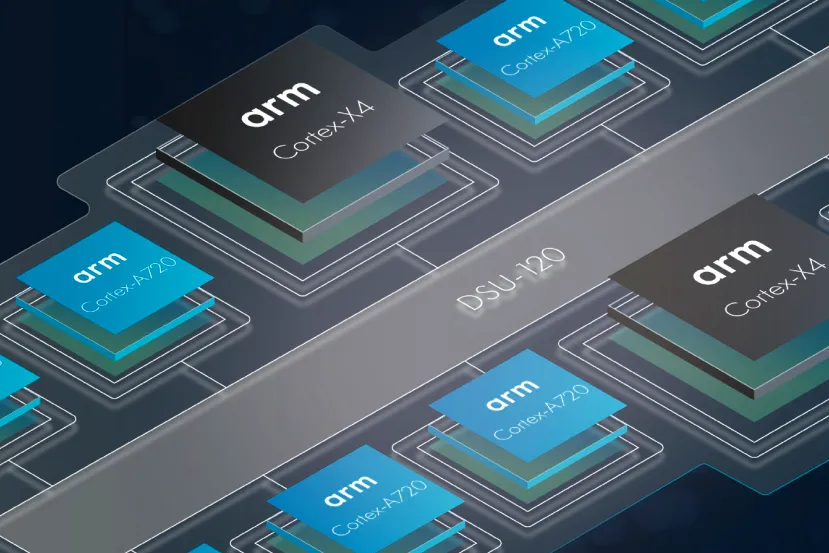

TCS23 y DSU-120: hasta 14 núcleos por clúster

Ahora que hemos visto las novedades que introduce cada uno de los núcleos por separado: Cortex-X4, Cortex-A720 y Cortex-A520, vamos a ver cómo funcionan en conjunto y las configuraciones y mejoras que ARM ha preparado para los SoC de próxima generación.

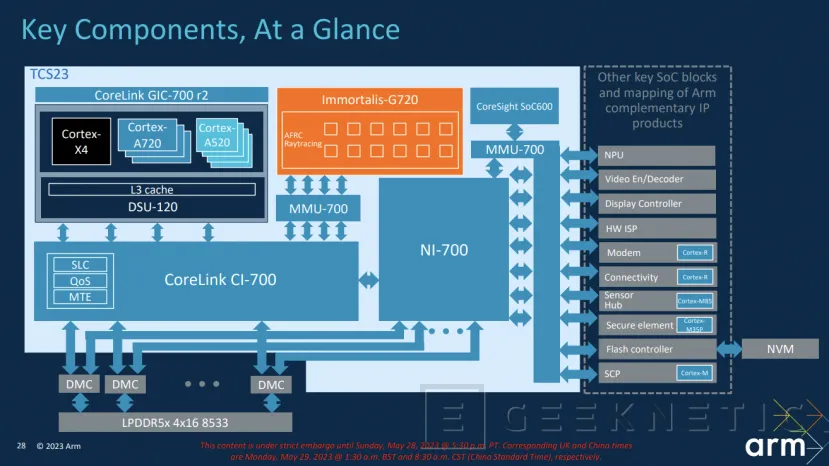

TCS23 es el nombre para la "Total Compute Solution" del 2023, es decir, el diseño base que combina todas las tecnologías de los núcleos que hemos visto hasta ahora junto a otros elementos como las nuevas GPU que explicamos en este artículo, el sistema DSU-120 para unir varios clústeres de núcleos y los CoreLink CI-700/NI-700 y MMU-400 para interconectar todos estos elementos con la memoria (LPDDR5X a 8.533 MHz soportada), ISP, Modem, NPUs ,almacenamiento y mucho más.

El esquema general del TCS23 es el siguiente, aunque las configuraciones de núcleos de la CPU puede variar según las necesidades de cada empresa.

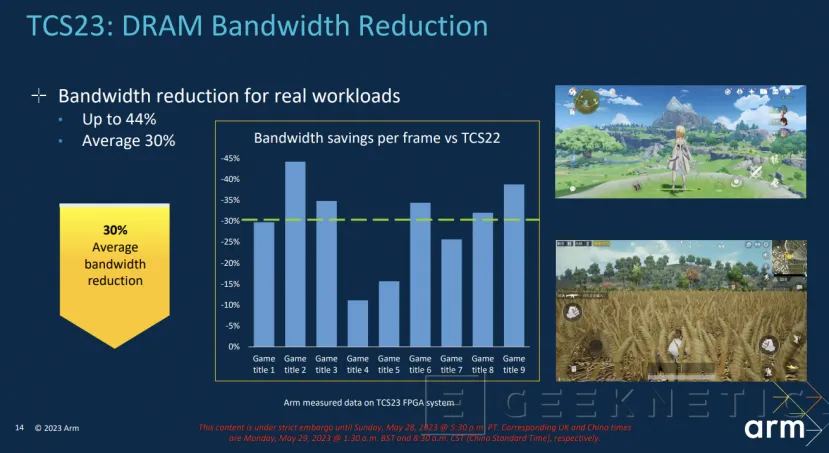

Este diseño consigue una reducción de ancho de banda de la memoria de hasta un 44%, con medias del 30%.

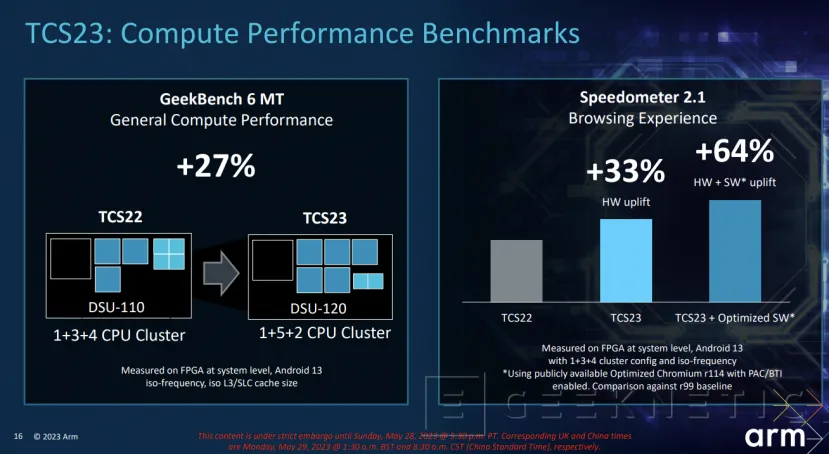

Por ejemplo, una configuración anterior (TCS22) de 8 núcleos con una distribución de 1+3+4 (X3, A715, A510) núcleos de pasada generación, con un TCS23 dotado de 1+5+2 (X4, A720, A520), consigue un 27% más de rendimiento en Geekbench 6 multinúcleo, y un 33% en experiencia de navegación con Speedometer 2.1.

Si añadimos mejoras software para adaptarse a la nueva arquitectura, podemos conseguir hasta un 64% más de rendimiento.

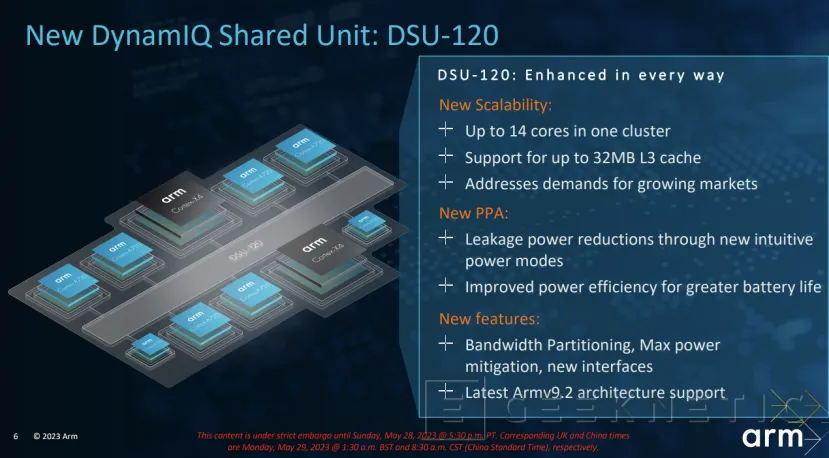

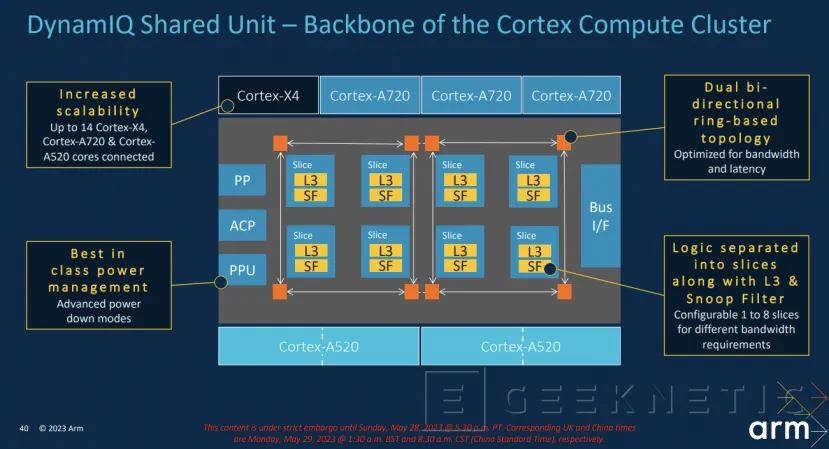

Uno de los aspectos clave de los nuevos SoCs que integrarán estas nuevas arquitecturas es el DSU-120 (DynamIQ Shared Unit), el sistema de interconexión de núcleos con el que se pueden conseguir clústeres de hasta 14 núcleos que comparten hasta 32 MB de caché L3.

Estos clústeres pueden combinar distintos núcleos Cortex-X4, Cortex-A720 y Cortex-A520 dependiendo de las necesidades del dispositivo y fabricante.

El DSU-120 es capaz tanto de funcionar con SoCs que tengan un único núcleo Cortex-A520 hasta sistemas con 14 núcleos, con combinaciones de 1+3+4 o incluso 10 núcleos Cortex-X4 y 4 Cortex-A720. Naturalmente, a mayor número de núcleos de altas prestaciones, mayor será el consumo y necesidades de refrigeración del SoC.

Es más, con el nuevo DSU-120 podemos tener hasta 14 núcleos Cortex-X4 en un único SoC. El procesador resultante de una configuración así sería muy superior en rendimiento a las propuestas de 1+4+3 o 1+2+5 por ejemplo. Pero su consumo y necesidades de refrigeración no lo harían apto para un smartphone o tablet pasivo y estaría orientado más para portátiles.

En cualquier caso, las posibilidades de esta arquitectura son enormes para los fabricantes que requieran SoCs de cualquier tipo de potencia o eficiencia.

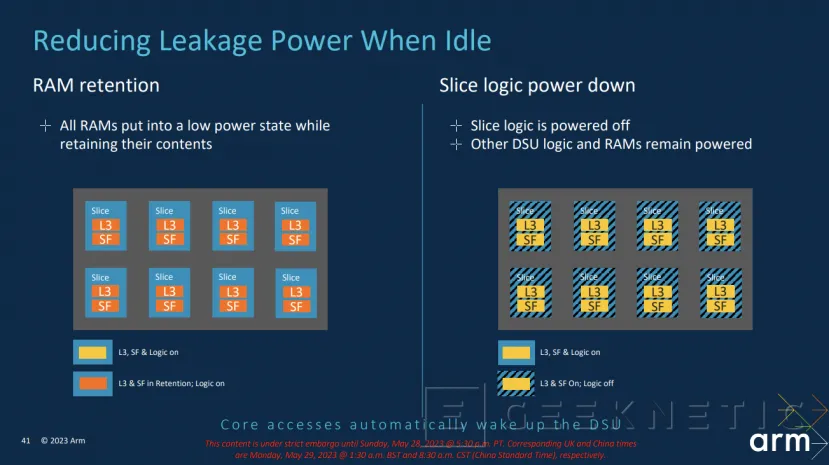

DSU-120 para las CPUs ARMv9.2 cuenta con un diseño que permite la reducción de consumo para adaptarse a tiempo real a las necesidades del momento. Hasta el punto de que es capaz de apagar o encender distintas partes de la memoria L3 de manera independiente.

El nivel de optimización de esta arquitectura de caché L3 dividida en partes es tal, que es posible desactivar la lógica de las distintas partes de la caché mientras permanecen activadas las cachés L3 que se comunican con la RAM, o también colocar en un modo de baja energía a las memorias caché para que mantengan sus datos sin apenas consumo mientras el resto del sistema funciona.

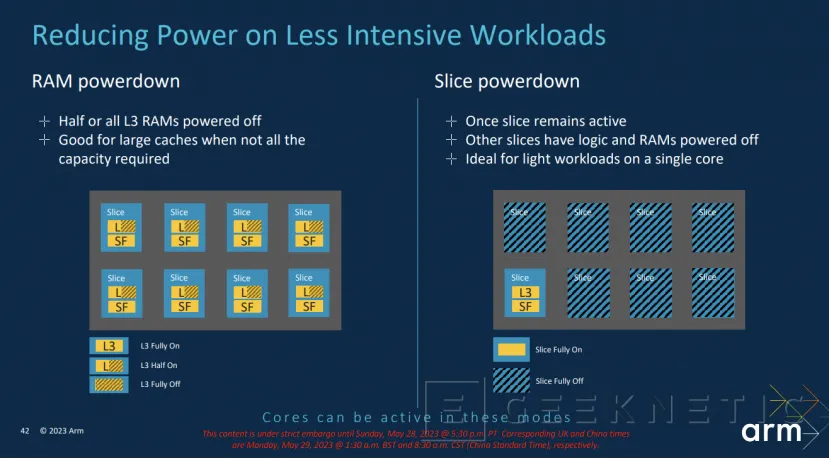

Incluso el DSU-120 puede apagar medio bloque de memoria caché L3 y dejar la otra parte encendida, lo que permite tener un SoC con una caché L3 de gran capacidad que consuma mucho menos cuando no es necesaria tanta memoria.

En aquellos casos donde se usen pocos núcleos, es posible apagar directamente toda la lógica y las cachés, dejando solamente encendidas las necesarias.

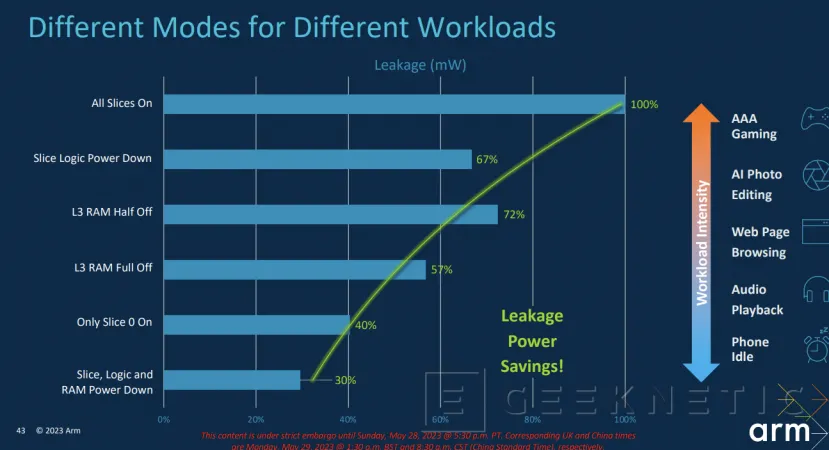

Estos modos de energía y de apagado total o parcial de las cachés y de sus lógicas, está directamente relacionado con el uso que tenga el sistema en cada momento. Por ejemplo, cuando se esté jugando a juegos con altas exigencias, todas las divisiones o partes en las que se divide la L3 y sus lógicas estarán activas al 100% y el consumo será el más alto. Conforme bajemos los requisitos, ya sea editando fotos, o navegando en la web, podrán activarse automáticamente los distintos modos de desactivación total o parcial de las L3 para ir ahorrando energía.

La combinación de los núcleos Cortex-X4, Cortex-A720 y Cortex-A520 junto al DSU-120 han permitido a ARM ofrecer el clúster de computación más potente de su historia, y también el que consigue mayores eficiencias energéticas.

Nuevos núcleos BlackHawk, Chaberton y Hayes para la siguiente generación

Estas han sido las novedades más interesantes en la nueva arquitectura Cortex y la plataforma TCS3 de ARM para este año, pero ARM también nos ha dejado ver los nombres y algunas tecnologías que veremos en el futuro.

El sucesor del TCS23 será el TCS24, que introducirá nuevos núcleos de CPU y demás elementos que formen parte de los próximos SoCs basados en la arquitectura de la compañía.

De esta forma, los núcleos más potentes, ahora representados por los Cortex-X4, tendrán el nombre en clave de "Blackhawk", mientras que los sustitutos de los Cortex-A720 serán los "Chaberton" y los de los Cortex-A720 serán los ARM "Hayes". Estos nombres son los nombres en clave internos de ARM, y es de esperar que cuando lleguen al mercado lo hagan manteniendo la denominación Cortex.

Por su parte, las GPU de nueva generación serán las Krake, y los CI-700 y NI-700 serán sustituidos por "Tower". Mientras que, por otro lado, los clúster de estos núcleos de CPU seguirán utilizando el mismo DSU-120 que se ha introducido en el TCS23.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!