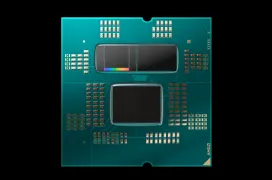

Aparecen más detalles acerca del AMD 3D V Cache y cómo conecta la caché a los CCDs

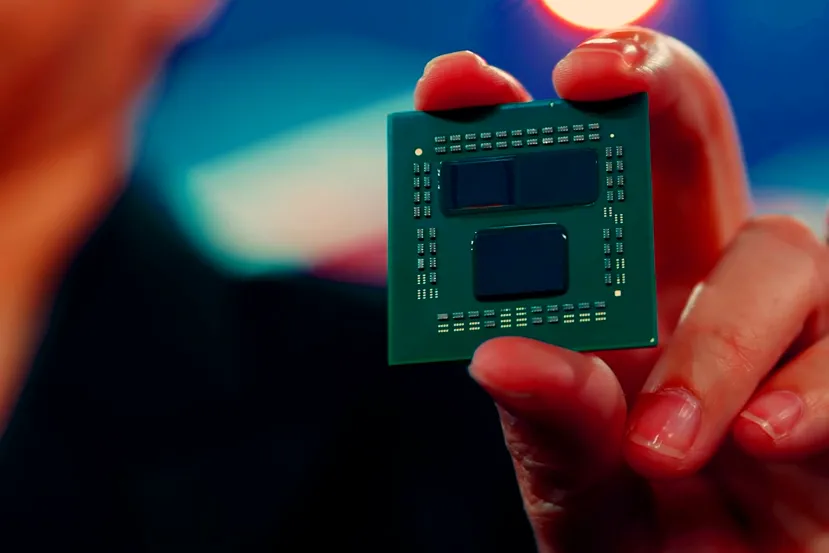

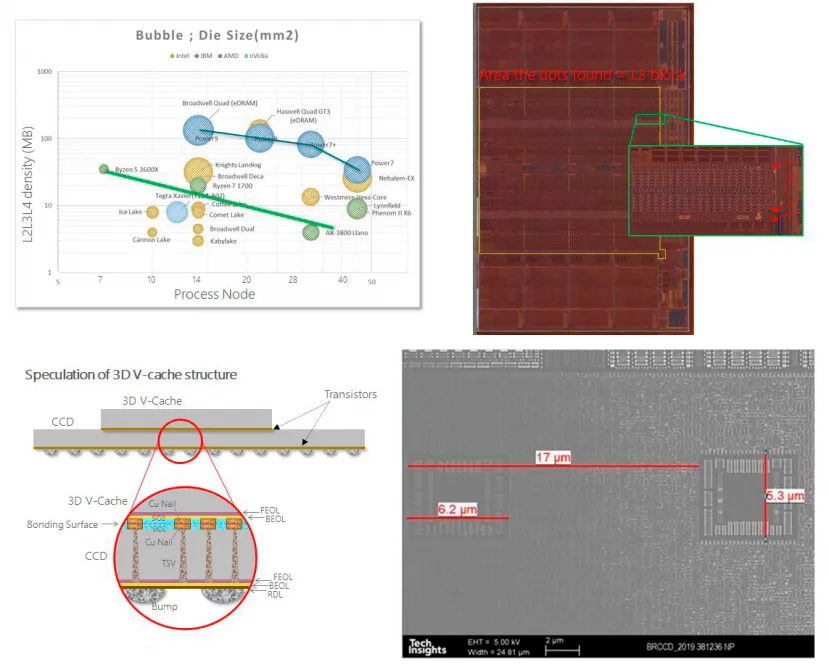

por Juan Antonio Soto 2AMD presentó una nueva tecnología de apilado llamada 3D Vertical Cache el pasado Computex, Lisa Su nos presentó un prototipo al que habían añadido una nueva caché uniendo dos CCDs mediante el sistema de unión directa cobre a cobre. Desde LinkedIn, Yuzo Fukuzaki nos muestra más detalles acerca de esta nueva tecnología 3D V Cache de AMD, ampliando la información que ya ofreció AMD unos días más tarde.

La teoría nos dice que esta nueva caché instalada en la parte superior de los CDD amplía la caché del CCD haciendo creer al sistema operativo que tiene una caché L3 de 96 MB en total en lugar de separarlo en una caché de cuarto nivel independiente. Esta caché de 64 MB está fabricada con el mismo proceso de 7 nanómetros del CCD con unas dimensiones de 6x6 mm y se coloca justo encima de donde está colocada la caché L3 en el CCD. Para conectarlos se usan 23.000 TSV de 17 micrómetros.

Gracias a esta nueva tecnología, se consigue hasta un 15% más de rendimiento en los juegos y estará disponible para finales de este 2021, quizá veamos esta nueva tecnología en los próximos procesadores con núcleos Zen 3+ antes de dar el salto al socket AM5.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!