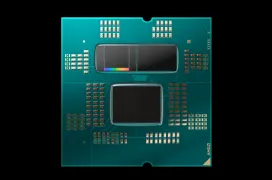

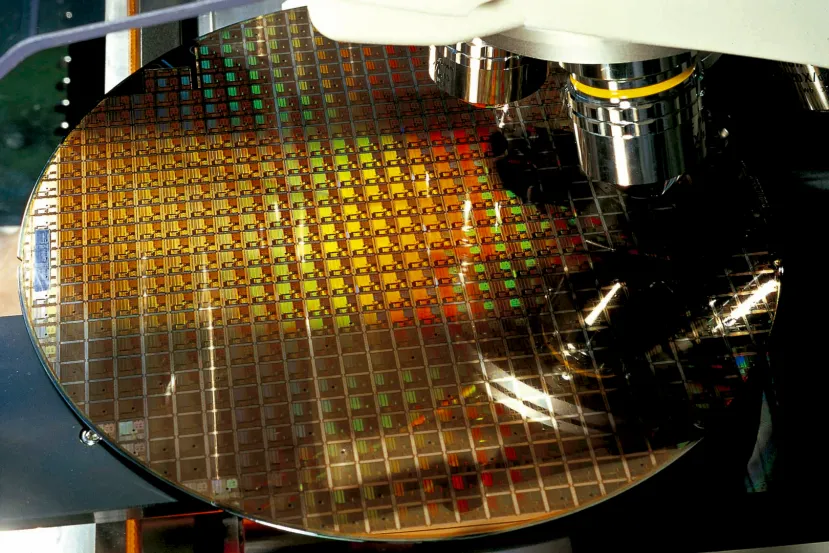

El nodo de 3 nanómetros de TSMC deja entrever que el escalado de SRAM está estancado

por Jordi BercialHace ya tiempo que estamos viendo como la reducción en el tamaño de los nodos de proceso está siendo cada vez más difícil, tanto a nivel de reducir el tamaño en sí mismo como a la hora de aumentar la densidad de las distintas zonas. Asimismo, cuando TSMC introdujo su gama de nodos de 3 nanómetros, sólo habló del escalado en las zonas lógicas de este proceso.

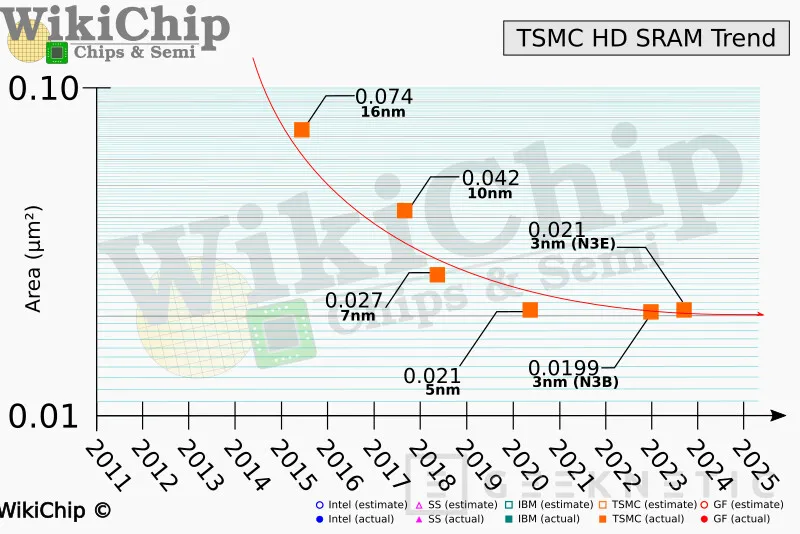

Esto tiene un motivo, y es que tal como podemos leer en TechPowerUp, parece ser que el escalado de la SRAM, la memoria que forma parte de la caché de los chips que utilizamos a diario, está estancado hasta el punto de que la densidad de esta memoria es prácticamente idéntica entre los nodos de 3 nanómetros y de 5 nanómetros de TSMC.

Supuestamente, TSMC indicó que la mejora de densidad era de 1.2 veces en la SRAM entre ambos procesos, pero finalmente la densidad real cuenta con una mejora de apenas un 5 por ciento, algo que empieza a complicar la justificación del coste de estos chips entre ambos nodos.

El escalado de la SRAM llevaba tiempo que no terminaba de seguir de cerca el escalado lógico, pero finalmente se ha visto completamente desacoplado en este último nodo, donde la mejora es nula.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!