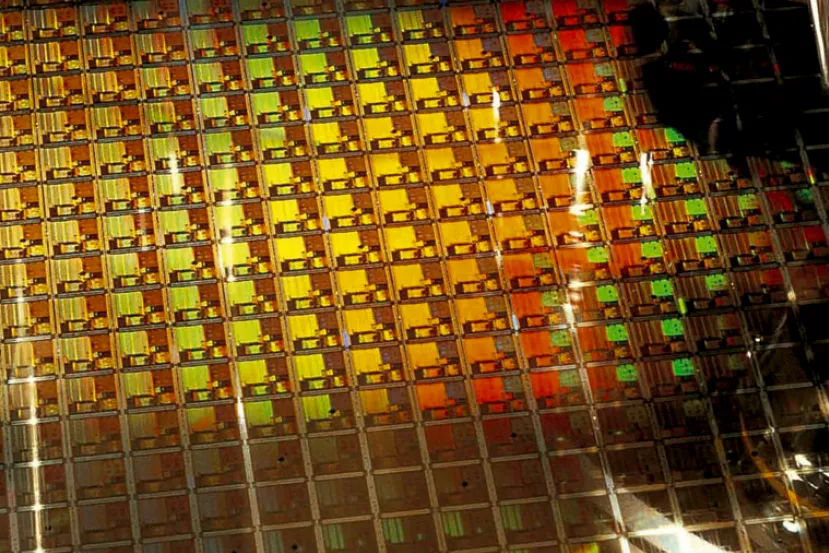

Los 2 nanómetros de TSMC prometen un 15% más de rendimiento y un 30% de reducción de consumo

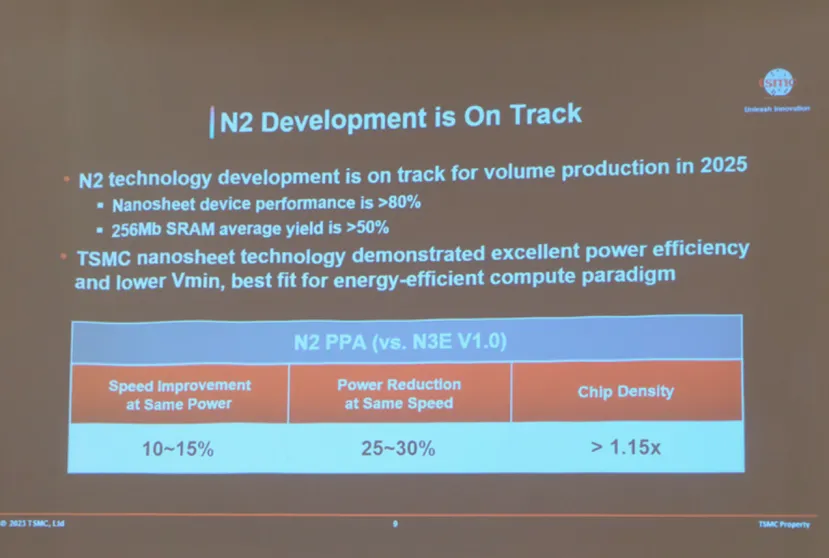

por Antonio DelgadoTSMC ha desvelado algunos detalles de su proceso de fabricación de 2 nanómetros. Este proceso, denominado TSMC N2 PPA, tiene prevista su llegada a lo largo del año 2025 ya en estado de fabricación en gran escala.

Según los plantes de la compañía y las pruebas que han ido realizando en la fase de diseño y testo, el paso del proceso de fabricación N3E de 3 nanómetros al proceso N2 PPA supondrá unas mejoras de rendimiento del 10 al 15% manteniendo el mismo consumo. En caso de mantener el mismo rendimiento, la reducción de consumo podrá alcanzar valores del 25 al 30 %.

Además, los 2 nanómetros de TSMC aumentarán en un 15% la densidad de los chips, es decir, permitirán un 1,15 veces más transistores en la misma área del chip fabricado respecto del proceso N3E.

Se espera que uno de los primeros clientes de los N2 de TSMC sea Apple, compañía que ya tendría reservada la mayor parte de la producción de 3 nanómetros del fabricante. De hecho, este acaparamiento por parte de los de Cupertino estaría haciendo que compañías que actualmente fabrican en TSMC como AMD o Qualcomm, se estén planteando dar el salto a otros fabricantes de chips como Samsung.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!